Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

??

MICROPROCESSORS

THE MOTOROLA GATEWAY BOARD

(MCF5202 Microprocessor To MC68EC000 Bus Interface Card)

Jeff Miller

October 15, 1997

1.0 Introduction

The integrated Gateway circuit board will bridge an existing MC68EC000 system to the new ColdFire?? MCF5202 VL-RISC microprocessor, to evaluate the possibility of moving toward a higher performance architecture. It can be used to evaluate system enhancements such as on-chip instruction and/or data cache and bursting to external memory. It can also be used to port software code to the ColdFire architecture directly in a customer???s system as opposed to the traditional method of porting code to an evaluation platform. This paper describes the use and opera- tion of the Gateway board as well as technical information that can be used as a reference design.

2.0Gateway Board Overview

2.1Software Considerations

The principal use of this board is to help port system software code from the M68000 architecture to the Cold- Fire architecture. Users will have to recompile the system software to target the MCF5202 instead of targeting the M68000. Even though the system will see a hardware interface that looks like a MC68EC000, the software must con- sist of ColdFire instructions for the MCF5202 to work properly. Refer to Section 8, ???Porting from M68K Architec- ture,??? of the MCF5202 User???s Manual for an overview of the issues encountered when upgrading from the M68000 to the ColdFire microprocessor. In addition, you???ll have to keep three key things in mind while porting system software code from the MC68EC000 system to the MCF5202 system

1.mapping 32-bit MCF5202 addresses to 24-bit 68EC000 addresses

2.cache coherency

3.RMW cycles

MOTOROLAGATEWAY BOARD1

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

cache mode to cache-inhibit. This will require the microprocessor to go to external memory to get accurate data as opposed to having a cache hit within internal memory which could possibly contain stale data.

2.1.3 RMW cycles

If the TAS instruction is used in the original M68000 code for implementing the locked or read-modify-write transfer sequence in hardware, then new code will have to be written that essentially implements the same locked transfer in software. This can be done by raising the interrupt mask to 7 and then executing the read, modify, and write instructions, and then lowering the mask back down to the appropriate level. This will ensure that the sequence of instructions between the raising and lowering of the mask will execute uninterrupted, except for a level 7 interrupt which is nonmaskable.

2.2 Hardware Considerations

The target system must have a female 68-pin PLCC socket such that it could hold a 68EC000 PLCC FN pack- age not a 68EC000 QFP FU package. The Gateway board has a male connector arranged in a PLCC FN fashion that will sit in this socket. The Gateway board can operate in 8- or 16-bit data mode. The board can handle interrupt acknowledge cycles for external vector number acquisition or the AVEC* signal can be used to allow internal vector generation. One difference between the MCF5202 and the 68EC000 is that DA*[1:0] is always asserted whether AVEC* is asserted or not. Also, the interrupt level being acknowledged is driven onto A/D[4:2] by the MCF5202, which has to be routed onto address lines A[3:1] for the 68EC000. See Figure 3 for more details. The board also has control logic to handle bus arbitration for alternate bus masters. If the HALT signal is asserted, the processor will stop bus activity at the completion of the current bus cycle and will place all control signals in the inactive state and place all three-state lines in the high-impedance state.

3.0 Performance

The Gateway board performance will be ???rst discussed generally and then speci???cally with an industry-stan- dard benchmark. For each bus cycle, there is one extra clock required from the beginning of the ColdFire MCF5202 microprocessor bus cycle to the beginning of the 68EC000 bus cycle. This is due to the multiplexed ATM signal on the ColdFire which is required to create the FC signals on the 68EC000 bus. Also, there are some bus clocks inherent to the ColdFire cycle that occur after the 68EC000 bus cycle is done. This is zero to two extra clocks, depending on the size of the access and whether the access is a read or a write. Therefore, because the fastest possible bus transac- tion for the 68EC000 is 4 bus clocks, the fastest Gateway board bus transaction can be as few as 5 bus clocks for the ???rst bus access of a longword write, or as many as 7 bus clocks if doing, for example, a single byte read. Table 2 and Table 3,compare all possible combinations of accesses between the MCF5202 and the MC68EC000.

MOTOROLAGATEWAY BOARD3

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

6.0 Bus Operation

The Gateway board supports a synchronous interface between the MCF5202 bus and the MC68EC000 bus. The waveforms in this document are meant to provide a functional description of the bus cycles required for data transfer operations. The examples below show a longword read and write to a 16-bit wide data bus of the MC68EC000 as well as an Interrupt Acknowledge Cycle. Note that at all times the MCF5202 will not burst (TBI*=0) and that the address phase lasts for only one clock (AA*=0).

Figure 1: Longword Read To A 16-Bit Port

CLOCK

TS*

R/W*

FC[2:0]

A[23:0]

6GATEWAY BOARDMOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

Figure 2: Longword Write To A 16-Bit Port

MOTOROLAGATEWAY BOARD7

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

Figure 3: Interrupt-Acknowledge Operation

AVEC*

IPL*[2:0]

8GATEWAY BOARDMOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

END

14GATEWAY BOARDMOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

9.0 Block Diagram

Figure 5: Gateway Board Block Diagram

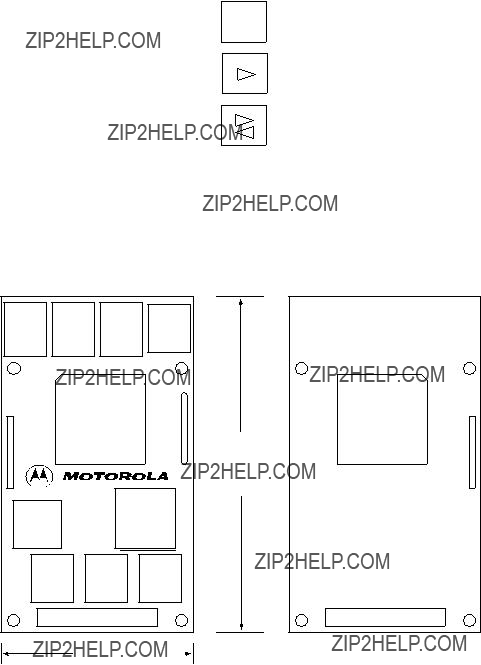

10.0 Gateway Board Physical Layout

Figure 6: Physical Layout (Actual Size)

2 in.

MOTOROLAGATEWAY BOARD15

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

11.0 Gateway Board Bill Of Material

Table 5: Bill Of Material

16GATEWAY BOARDMOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

12.0 ColdFire Gateway Board Schematics (1 of 2)

Freescale Semiconductor, Inc.

ISPEN GND

10 PF

VCC

GND

GND

33 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

BYPASS FOR U1

FOR U2 - U9

VCC

GND

GND

0.1 UF

VCC

GND

GND

0.1 UF

VCC

GND

GND

MOTOROLAGATEWAY BOARD17

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

ColdFire Gateway Board Schematics (2 of 2)

Freescale Semiconductor, Inc.

18GATEWAY BOARDMOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Freescale Semiconductor, Inc.

convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its of???cers, employees, subsidiaries, af???liates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such

MOTOROLAGATEWAY BOARD19

For More Information On This Product,

Go to: www.freescale.com

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND